\_\_\_\_\_

# Design And Analysis Of Low Power 6t Full Adder With Finfet Technology

M.Chandra Sekhar Reddy<sup>1</sup>, Dr. P.Ramana Reddy<sup>2</sup>

<sup>1</sup>(Research scholar ,ECE Department,JNTUA University , Anantapuramu, India, A.P.) <sup>2</sup>(Professor,ECE Department,JNTUACE, Anantapuramu, India, A.P.) *Corresponding Author: M.Chandra Sekhar Reddy*

**ABSTRACT**—Full adder is the basic and most common element in the designing of basic arithmetic circuits like Adders, Multipliers, and Dividers etc. It is the heart of Arithmetic and Logic Unit. Any change in the adder cell will degrade the overall performance of the designed circuit, so high care must be taken while designing these adders cells. This paper proposes a new design using FinFETs with 2T XOR gate based 6T full adder. A comparison is also made on the basis of area, power and delay to find out the best possible design technique. **KEYWORDS:** XNOR gate, Full adder, FinFET Technology, delay, power Dissipation.

Date of Submission: 17-02-2018

Date of acceptance: 05-03-2018

# I. Introduction

\_\_\_\_\_

A full adder is a center unit in a significant number of the electronic devices that perform numbercrunching and intelligent operations. It is the fundamental component in a considerable lot of complex numbercrunching circuits like adders, multipliers, dividers, exponentiation, comparators equality checkers. A large portion of the VLSI applications, for example, Digital Signal Processing (DSP), picture handling, video preparing and chip broadly utilize math operations. Parallel expansion is considered as the most pivotal and critical piece of the number juggling unit since all other math operations include expansion[1]. In this way, making the full adder cell effective, diminishing its postponement, territory and expanding , its speed will decrease the general deferral of the entire framework.

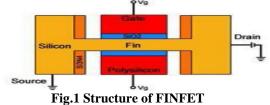

The principle center of the work displayed here is to analyze distinctive full adder plan philosophies and to present another outline method which is a FinFET based full adder with 2T XOR entryway. FinFET implies Fin Field Effect Transistor. FinFET is a Non Planar Dual Gate Transistor utilized as a part of the Silicon Architecture which comprises of extensive computational thickness. FinFET was begat by Berkeley specialists of the college of California and it was produced for the utilization of Silicon-on-Insulator.

FinFET innovation takes its name from the way that the FET structure utilized resembles an arrangement of balances when seen. The principle normal for the FinFET is that it has a leading channel wrapped by a thin silicon "blade" from which it picks up its name. The thickness of the balance decides the viable channel length of the device. The structure of FINFET as Shown in Fig 1[2]. FINFET transistor innovation is another idea to the VLSI fashioners. The main FINFET was manufactured a two-entryway on SOI structure as called a solitary door transistor. FINFET term was clarifying the non planar, two-entryway transistor demonstrate. The most important attributes of FINFET that the channel shaped between the source and deplete because of the electron stream conduction is secured with a thin silicon "fin" which execute the body of the transistor.

## II. Exiting Full Adder Designs

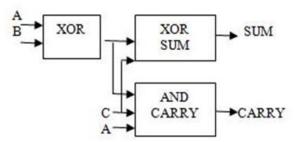

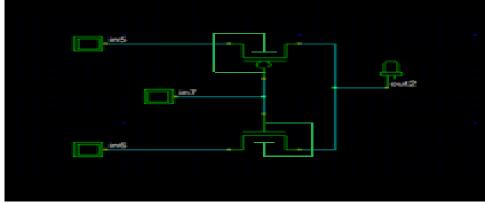

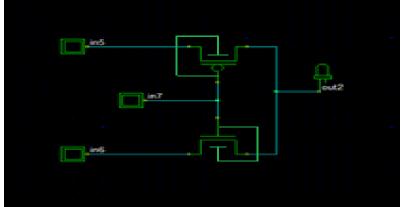

Half breed adders comprise of more than one logic styles in its usage they are ordered in different classes relying on their yield structure and flags. Fundamental plan approach for Hybrid Full Adder is appeared beneath fig.2[3].

Fig.2 Basic Design Approach for Hybrid Full Adder.

### A. GDI FinFET Full Adder

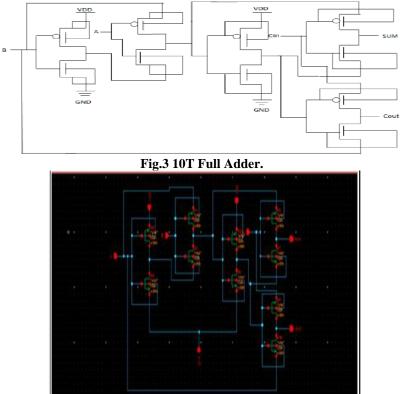

The Gate Diffusion Input Technique diminishes both deferral and power.GDI FinFET full adder comprises of three info pins and two yield pins. Here we are utilizing shorted door FinFET as indicated by the methods of operation. The supply voltage is taken as 0.7V for GDI FinFET utilizing the rhythm Virtuoso device at 15nm innovation. In GDI[4] FinFET multiplexer is taken as specific information. Multiplexer resembles a reversed keeping in mind the end goal to produce the convey articulation, we certainly utilize multiplexer. FinFET GDI doesn't accomplish full swing as a result of the limit voltage misfortune. Another explanation behind GDI FinFET is we are taking three contributions without the utilization of VDD and GND. Rationale Circuit and schematic of 10T full adder is appeared in beneath fig. 3. What's more, fig 4.

Fig.4. Schematic of 10T Full Adder.

### **B.8T Full Adder**

8T Full Adder technique depends on the utilization of a basic cell as appeared in underneath fig.5. XOR and XNOR capacities are the key factors in snake conditions. On the off chance that the age of them is streamlined, this could enormously improve the execution of the full adder cell. a run of the mill Full Adder in 8T rationale exemplifies just 8transistors and the quantity of interconnections between them is profoundly decreased. Having every transistor a lower interconnection capacitance, the W/L can be near the base esteem and the power utilization is diminished[5].

Fig 5. 8T Full adder with FinFETs.

## III. Proposed 6t Full Adder With Finfets

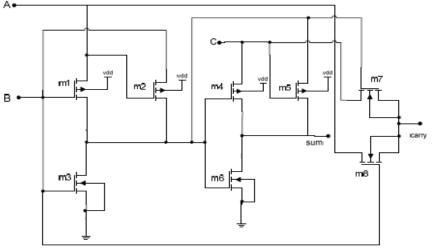

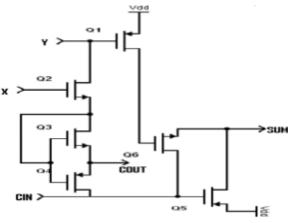

The proposed full adder operation should be possible with 6 transistors itself. Here a 2 transistor XOR gate is the essential part and subsequently two XOR gates have been utilized. Schematic of 2T XOR gate is appeared underneath fig.6. XOR gate plan it comprise of 2 transistors Q1 and Q2 with A, B as sources of info, when inputs A and B both are rationale low then Q1 is in ON state and Q2 is in OFF state so the yield is low, when inputs An is low and B is high then Q1 is in OFF state and Q2 is in OFF state so the yield is at high similarly if the information An is high and B is low then Q1 is in ON state and Q2 is in OFF state so the yield is at high, yet when both the data sources are at high at that point yield is at low thus the above circuit goes about as XOR gate[6].

Fig 6.Proposed 2T XOR gate with FinFETs.

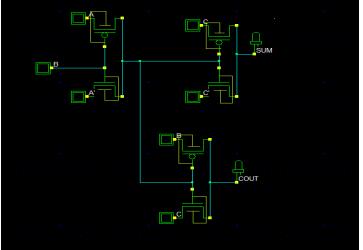

## **6T Full Adder with FinFETs**

By decreasing the quantity of transistors utilized, an expansion of speed in dataflow has been accomplished. Likewise the diminishment in the transistor use has prompted a decrease in the zone and power utilization. The proposed demonstrate is appeared in Fig.7[7]. Reality table of Full Adder is appeared in beneath table. 1

Fig 7. 6T Full Adder with FinFETs.

Table 1: Truth table for full adder

| Α | В | Cin | SUM | Cout |

|---|---|-----|-----|------|

| 0 | 0 | 0   | 0   | 0    |

| 0 | 0 | 1   | 1   | 0    |

| 0 | 1 | 0   | 1   | 0    |

| 0 | 1 | 1   | 0   | 1    |

| 1 | 0 | 0   | 1   | 0    |

| 1 | 0 | 1   | 0   | 1    |

| 1 | 1 | 0   | 0   | 1    |

| 1 | 1 | 1   | 1   | 1    |

The XOR gate and multiplexer are essential building obstructs in full adder plan. Number-crunching operation of the proposed circuit relies upon the execution of XOR and multiplexer pieces. The better approach for configuration ought to have less number of transistors to actualize XOR circuits[8] for low power dispersal.

The multiplexer circuit MUX is utilized as a part of our proposed configuration to produce Cout. Transmission entryway is utilized as a 2 to 1 multiplexer. The transmission entryway has two focal points for the circuit: right off the bat, it accelerates the convey proliferation as a cushion along the convey chain. Besides, it gives; the transmission entryway can enhance the yield voltage swing as a level reestablishing the circuit.

The proposed full adder circuit, which utilizes two XOR gates and one multiplexer, requires six transistors. Fig (7) speaks to a full adder circuit, it has 6 quantities of transistors i.e. Q1, Q2, Q3, Q4, Q5 and Q6. Transistor Q1 and Q2 go about as XOR gates, Q3 and Q4 additionally go about as a Second XOR gate. In this circuit AND gatess and additionally gates of full adder supplanted with a multiplexer, rather than utilizing pass transistor rationale to speak to multiplexer in the above circuit a transmission door is utilized which goes about as a 2:1 multiplexer. Here the yield of first XOR gate is connected as a contribution to the following XOR gate, second XOR gate has C as second info and deliver the SUM as yield[8].

### **IV. Results And Discussions**

The execution measurements of the full Adder measured are power, postponement and vitality. The reenactment examination is done over CADENCE DESIGN SUIT 12.1 Tool. The reproduction investigation is completed with three sources of info (A, B, C) and two yields (Sum and Carry) of full Adder. The recreation waveform of energy, postponement and vitality of FinFET based circuits is talked about. Schematic of the Proposed 2T XOR [9]door and 8T full snake is appeared underneath fig.7.and fig 8.

Fig 7. Proposed 2T XOR gate with FinFETs.

Fig 8. 6T Full Adder with FinFETs

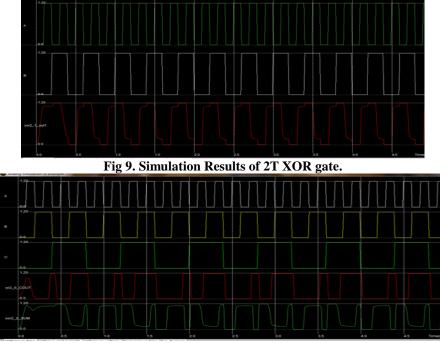

The simulation results of 2TXOR gate are shown in below in fig 9.

Fig 10. Simulation Results of 6T Full Adder.

Table:1 demonstrates the execution examination of the adder circuits. In view of the execution investigation, it is watched that the 10T FA is low power dissemination with more postponement. 6T FA is unrivaled as far as low power dispersal and fast, in the meantime, for the same working conditions, The required adder can be browsed the execution investigation table1 to meet the plan particulars, for example, low power scattering, less deferral.

| Tustelt comparative study of fired and rower of various run frader 2 esigns |                               |                              |  |  |

|-----------------------------------------------------------------------------|-------------------------------|------------------------------|--|--|

| ALU Designs                                                                 | Proposed 6T Full Adder design | Exiting 8T Full Adder Design |  |  |

| Power Consumption(mW)                                                       | 0.75                          | 1.185                        |  |  |

| Propagation Delay(nS)                                                       | 0.006                         | 0.166                        |  |  |

| Power Delay Product(j)                                                      | 0.0045                        | 0.197                        |  |  |

| Tomer Benaj Houder())                                                       | 010018                        | 011) (                       |  |  |

Table1. Comparative Study of Area and Power of Various Full Adder Designs

## V. Conclusion

In this paper power and zone productive plan of full adder with 6 transistors utilizing proposed 2 transistors XOR gate has been displayed. The attributes of the proposed full adder circuit are looked at against before revealed full adder circuits in view of power utilization. Full adder demonstrates the power utilization of 0.75MW and better yield flag levels with the diminished transistor count.

### References

- T. J. K. Liu, —FinFET—history, fundamentals and future, I in Proceedings of the Symposium on VLSI Technology Short Course, University of California, Berkeley, Calif, USA, June 2012.

- [2]. Vita Pi-Ho Hu, Ming-Long Fan, Chien-Yu Hsieh, pins, andChing-Te Chuang, —FinFET SRAM Cell Optimization Considering Temporal Variability Due to NBTI/PBTI, Surface Orientation and Various Gate Dielectricsl, IEEE Transactions on Electron Devices, VOL. 58, NO. 3, pp.805-811, march 2011

- [3]. Wen-TsongShiiie, -Leakage Power Estimation and Minimization in VLSI Circuitsl, IEEE 2001

- [4]. Korea Ravi Kumar, P. Narsimulu, A. Santhosh Kumar, M. Raju "A novel 3 transistor or gate based, full adder design for VLSI applications" Proceedings of RACVES\_2014, Warangal, T.G.

- [5]. Sanjeev Kumar, Pankaj Yadav, "Design of a six transistor Full adder cell for VLSI applications. "International journal of research in computer applications and robotics, Vol.1, no.8, pp.15-21, November 2013.

- [6]. Wang J.M, Fang S.M and Feng, W.S New efficient designs for XOR and XNOR functions on the transistor level, IEEE J. Solidstate Circuits, 29 (7), 1994, 780–786.

- [7]. A. Chandrakasan, W. Bowhill, and, F. Fox, —Design of High Performance Microprocessor Circuitsl, IEEE Journal of Solid-State Circuits, Vol.36, No.10, pp. 263 -271, Aug. 2001.

- [8]. Jin-Fa Lin, Y.T. Hwang, M.H.Sheu and C.C.Ho, "A Novel High-Speed and Energy Efficient10-Transistor Full Adder Design, IEEE transactions on Circuits and Systems, vol. 54, no. 5pp.1050.1059, May 2007.

- S. Jim Hawkins on, "Analysis and Performance Comparison of CMOS and FINFET for VLSI applications" International Journal of Emerging Technology and Advanced Engineering Volume 3, Issue 2, February 2013.

- [10]. M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS full-adders for energy-efficient arithmetic applications," IEEE Trans. Very Large Scale Integration (VLSI) Systems., vol. 19, no. 4, pp. 718–721, Apr. 2011

- [11]. Tushar Surwadkar, IJETT-2014, "Upgrading the performance of VLSI Circuits using FinFETs"

- [12]. R. Uma, V. Vijayan, M. Mohanapriya, and S. Paul, "Area, delay and Power comparison of adder topologies," International Journal of VLSI Design & Communication Systems (VLSICS) Vol. vol. 3, p. 161, 2012.

- [13]. Prathima, N., and K. HariKishore. "Design of a low power and high Performance digital multiplier using a novel 8T adder." International Journal of Engineering Research and Applications, (JJERA) 3, no. 1(2013): 1832-1837.

- [14]. Ajay N. Bhoj, Niraj K. Jha, "Design of Logic Gates and Flip-Flops in High-Performance FinFET Technology". IEEE Transactions on Very Large Scale Integration (VLSI) Systems (Volume:21, Issue: 11), January 2013.

- [15]. Rahil Kumar, Kanika Sharma, Umesh Dutta, Design of Arithmetic and Logical Unit (ALU) Using FinFET, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 5, Issue 5, May 2016.

International Journal of Engineering Science Invention (IJESI) is UGC approved Journal with Sl. No. 3822, Journal no. 43302.

M.Chandra Sekhar Reddy "Design And Analysis Of Low Power 6t Full Adder With Finfet Technology" International Journal of Engineering Science Invention (IJESI), vol. 07, no. 03,

2018, pp 15-20.